### 科技部

# 111 年度「關鍵新興晶片設計研發計畫」說明附件二

#### 人工智慧(AI)晶片設計環境與服務

TSRI 提供下列 AI 晶片設計平台之一站式服務,包括 EDA 軟體/IP 使用服務、軟硬體協同驗證環境使用服務、AI 晶片設計技術諮詢/協同設計服務、AI 晶片製作與封裝服務、展示系統開發諮詢服務。

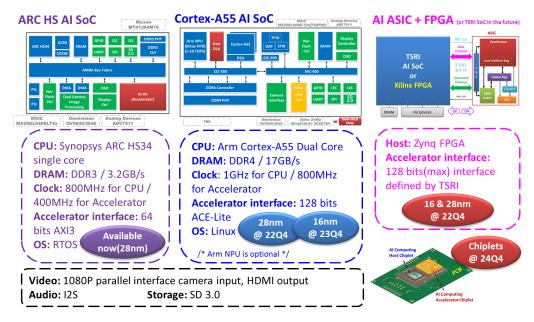

1. 多計畫 AI SoC 設計平台 (28nm/16nm)

TSRI 提供 2 種多計畫 AI SoC 設計平台,包括(1) ARC HS AI SoC 設計平台 以及(2) Cortex-A55 AI SoC 設計平台,規格及預定服務時程如下圖。學界 團隊使用上述平台設計之 AI SoC 之下線梯次原則上 1 年 1 次,TSRI 會視情況整合多個團隊的電路至同一個 AI SoC 進行下線。平台使用者可能需要 TSRI 協作服務,建議計畫提出前與 TSRI 先行討論。

針對 MCU 等級或非上述平台的 SoC 設計者,TSRI 可提供 IP 使用服務(僅限於 EDA Cloud 上使用且 TSRI 不提供技術諮詢服務)。目前可提供之 IP 包含 Arm Academic Access 資料庫內的項目(註1),Synopsys ARC HS/EM 系列 CPU 以及 EV Vision Processor,Andes RISC-V CPU。

註 1: <a href="https://armkeil.blob.core.windows.net/developer/Files/pdf/research/arm-academic-access-data-sheet.pdf">https://armkeil.blob.core.windows.net/developer/Files/pdf/research/arm-academic-access-data-sheet.pdf</a>

2. AI ASIC 及 FPGA 混合設計平台 (28nm/16nm/Chiplets)

簡化版的 AI SoC 設計平台,主系統(Host)為 Xilinx FPGA, AI 運算經由 TSRI 定義的介面卸載到學界團隊的 AI ASIC。ASIC 內有 PLL, 避免 Clock 受 IO Pad 限制。TSRI 會提供介面規格與電路以及 FPGA 端的軟/韌體以加速學界應用展示系統開發。學界團隊使用此平台設計之 AI ASIC 之下線梯次原則上1年1次, TSRI 會視情況整合多個團隊的電路至同一個 AI ASIC 進行下線。

TSRIAI晶片設計平台規格與預定服務時程

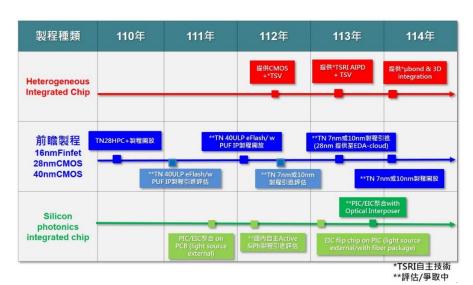

#### 前瞻製程平台服務

TSRI 提供包含數位/類比/RF/混合訊號等電路設計環境與設計套件,並配合本中心晶片實作服務提供 TSMC 16nm FFC、28nm HPC+製程及 TSMC 40G 製程晶片實作服務,亦可配合研究團隊之需求提供獨立梯次 16nm/28nm/40nm/65nm之 Shuttle 給予研究團隊進行晶片製作。在65nm 製程 Shuttle 可額外提供 Flip Chip 選項之自費晶片下線與 DRC 驗證技術諮詢。配合此計畫預計於111 年進行 TSMC 40nm EmbFlash 製程與 PUF IP 的引進評估及環境驗證,預計於112 年開始提供服務。參考111 年上半年 TSMC Shuttle 時程,約每兩個月提供一梯次 TSMC 40nm EmbFlash 製程 Shuttle,引進此製程後將依照經費與團隊需求規劃晶片實作服務之梯次,如下表所示。

前瞻製程常規梯次列表

| 製程種類                                              | 年度常規梯次               |  |  |

|---------------------------------------------------|----------------------|--|--|

| TSMC 16nm FFC                                     | 2                    |  |  |

| TSMC 28nm HPC+                                    | 111 年 2 梯 112 增至 3 梯 |  |  |

| TSMC 40G                                          | 4                    |  |  |

| TSMC 40ULP (EmbFlash*)                            | 2                    |  |  |

| TSMC 65nm                                         | 6**                  |  |  |

| 註:*EmbFlash 仍需配合 TSMC 廠內的時程,**TSMC shuttle 間隔為兩個月 |                      |  |  |

在 16nm FinFET 製程,TSRI 也將建立 FinFET Layout Dependent Effect 設計流程與進階版之 Dummy Fill 整合程式以加速全晶片之 DRC 驗證流程。同時也將提供 16/28nm 製程在射頻電路模擬所需之 EM 模擬環境,搭配 iPDK 建立與 EM 整合之設計環境。

計畫於 112 年進行 TSMC 10nm/7nm 製程的引進評估,並預計於 114 年開始提供服務。參考 111 年上半年 TSMC Shuttle 時程,111 年上半年有兩梯次之 7nm 製程 Shuttle,引進此製程後將依照經費與團隊需求規劃晶片實作服務之梯次。

前瞻與異質整合晶片製程服務

## 先進封裝(2.5D/3D)技術服務

目前 TSRI 可提供學術界 2.5D/3D 異質整合晶片技術諮詢服務包含:

- 1. IPD、2.5D 中介層(interposer)和電路板設計諮詢及製作

- 2. 晶片級植金球(gold stud)

- 3. 晶片級覆晶(flip chip)封裝

已規劃於 111~114 年進行之項目如下:

- 0.18μm CMOS backside TSV 開發,此技術除了可適用於生醫及影像晶片於

2.5D 異質整合晶片外,亦可當作感測、讀取、AI、電源管理等晶片之中介層使用

- 2. 評估晶片級 400 接腳 50μm-pitch micro bump 覆晶對接技術的可行性後,開

發此 400 接腳晶片與上述中介層覆晶對接技術

3. 提供學術團隊中介層與電路板(PCB)打線(wire bond)/覆晶對接及晶片與中介層打線/覆晶對接製作技術諮詢

#### 開發及提供服務時程規劃如下:

|                                    | 111年                           | 112年                         | 113年                          | 114年                        |

|------------------------------------|--------------------------------|------------------------------|-------------------------------|-----------------------------|

| IPD                                | WIPD                           | WIPD                         | WIPD                          | WIPD                        |

| CMOS<br>backside TSV               |                                | 0.18μm CMOS<br>v.1*          | 0.18μm CMOS<br>v.2**          | 0.18μm CMOS<br>v.2**        |

| RDL<br>Interposer                  | 1 layer<br>(W/S=20/20μm)       | 6 layers                     | 6 layers                      | 6 layers                    |

| 對接ASIC<br>pad數目及 pad<br>pitch (μm) | <20;<br>100                    | <40;<br>100                  | <40;<br>50                    | >400;<br>50                 |

|                                    | CMOS readout Sensor interposer | GelN CMOS Sensor O 18µm CMOS | CIS army sky Semon interposer | GIS Sensor Al CMOS II IIIII |

<sup>\*</sup>v.1 TSV 直徑  $40\mu m$ ,搭配錫球 50um,預計於 111 年底完成開發,112 年開始提供每年兩個梯次製作服務

<sup>\*\*</sup>v.2 TSV 直徑  $10\mu m$ ,搭配 Cu pillar 10um,預計於 112 年底完成開發,113 年開始提供每年兩個梯次製作服務

# Electronic integrated circuits (EIC)/photonic integrated circuits (PIC) 服務架構與高速傳輸介面量測

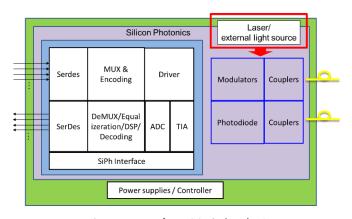

針對高速無線晶片、高速傳輸介面、PAM4(4級脈衝幅度調製)調制模式互聯系統實現在 100GE-800GE 傳輸應用提供整合驗證服務平台。平台技術規格將循指標性協會如 100G Lambda MSA 和 IEEE 802.3 在單通道、4通道的 200GE 光電模塊和 8 通道的 400GE 光電模塊等作規畫,實現包含:Electrical transceiver、Electrical receiver、Optical transmit path 技術、收發介面串接技術、Optical receive path 技術等,技術架構如下圖所示。

EIC/PIC 技術實現模塊架構圖

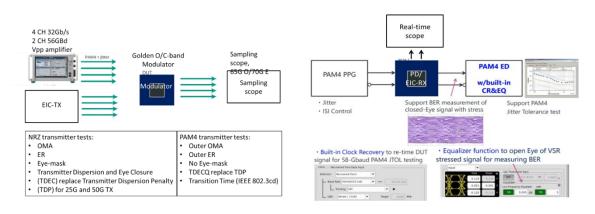

在測試服務方面,遵循各協會標準規格書中訂定規格,提供完整光電測試/驗證環境,如單通道 128GBaud Bit Error Rate(位元誤碼率)測試,依照協會規範的各種測試參數,進行與該晶片支援之資料傳輸率下的指定壓力訊號規格,另外如收發端的光(65GHz)/電(70GHz)眼圖分析,包含 Jitter、Skew、SSC、Rise/Fall Time等訊號測試。發射端與接收端測試驗證服務架構分別如下兩圖所示。

TSRI 提供之發射端測試驗證架構

TSRI提供之接收端測試驗證架構